La línea piloto NanoIC tiene la ambición de convertirse en la línea piloto profesional de I+D del mundo más allá de la tecnología de semiconductores.

Su objetivo es fortalecer el liderazgo de Europa en el ecosistema global de semiconductores y apoyar la visión de la Ley Europea de Chips para impulsar la innovación en mercados clave como la informática, las comunicaciones, la movilidad, la energía y la salud. La línea piloto NanoIC sirve como un puente importante entre la investigación de vanguardia y las aplicaciones comerciales, desempeñando un papel central en el fortalecimiento de la posición de Europa a la vanguardia de la innovación y la competitividad de los semiconductores.

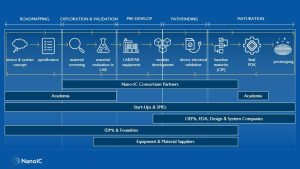

Un conducto robusto entre el laboratorio y la fábrica es esencial para cerrar la brecha entre la innovación en investigación y la comercialización en la industria de los semiconductores. La línea piloto NanoIC acelera la innovación en arquitecturas de sistemas informáticos mediante la maduración de tecnologías de semiconductores específicas. El objetivo es permitir que las empresas europeas sigan liderando la innovación en semiconductores.

Específicamente, la línea piloto NanoIC proporciona una línea piloto de sistema en chip (SoC) más allá de 2 nm para el desarrollo y maduración de tecnologías avanzadas de lógica, memoria y interconexión seleccionadas. El proyecto se centra en el desarrollo de capacidades a gran escala, la I+D colaborativa, la maduración de tecnologías avanzadas para la creación de prototipos y el apoyo a la innovación, particularmente en la sala limpia de imec en Lovaina (Bélgica), proporcionando acceso a estas tecnologías avanzadas en todo el ecosistema de semiconductores. Los participantes, independientemente de su papel en la cadena de valor, pueden abordar la línea piloto NanoIC de la manera que mejor se adapte a sus necesidades específicas y objetivos de innovación. Esto permitirá conocer tempranamente las áreas emergentes y ayudará a Europa a seguir siendo competitiva en toda la cadena de valor de los semiconductores, desde materiales, equipos, procesos y dispositivos hasta diseños y sistemas.

Consorcio NanoIC

El consorcio del proyecto de la línea piloto NanoIC está liderado por imec, junto con CEA-Leti de Francia, Fraunhofer Gesellschaft (FhG) de Alemania, el Centro de Investigación Tecnológica VTT de Finlandia, el Laboratorio Nacional Tyndall de Irlanda y el Centro de Ciencia de Superficies y Nanotecnología de la Universidad Tecnológica de Bucarest de Rumania. Cuenta con el apoyo del gobierno flamenco, otros países participantes y Chip Joint Venture. Todos los socios trabajarán juntos para garantizar la implementación exitosa de la línea piloto.

Componentes básicos de los futuros sistemas informáticos

Se espera que los dispositivos lógicos de clase Nanosheet mejoren el escalado y el rendimiento a lo largo de tres generaciones adicionales (N2, A14 y A10). Actualmente se prevé que las arquitecturas de transistores de efecto de campo complementarios (CFET) se introduzcan en el nodo A7 alrededor de 2031 y representen un importante punto de inflexión en el diseño de dispositivos CMOS. Los avances en este campo requieren una investigación exhaustiva de nuevos materiales, módulos de proceso, equipos y capacidades avanzadas de creación de patrones, que es donde entra en juego la litografía ultravioleta extrema (alta NA EUV) de alta apertura numérica.

Las innovaciones en memoria se centran en nuevas memorias magnéticas, más específicamente en la memoria de acceso aleatorio magnético de torsión de órbita de giro (SOT-MRAM) y en la memoria de acceso aleatorio dinámico integrada (eDRAM). Para este último, se están desarrollando configuraciones alternativas de 2T0C, incluida la exploración de semiconductores de banda prohibida amplia, como óxidos semiconductores como el óxido de indio, galio y zinc y dicalcogenuros de metales de transición 2D, que se han mostrado prometedores como materiales de canal alternativos. Paralelamente, el desarrollo de plataformas de memoria 3D que exploren nuevas opciones de memoria futuras para aumentar SRAM y DRAM es esencial para abordar los desafíos de capacidad de memoria y ancho de banda de memoria que plantean las nuevas cargas de trabajo.

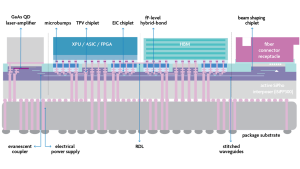

La integración de varios troqueles en un sistema requiere interconexiones eléctricas y ópticas avanzadas de 2 nm o más. Para avanzar aún más en las interconexiones eléctricas, será posible la integración heterogénea 3D, como las técnicas de unión híbrida de matriz a oblea (D2W). Para conectar eléctricamente el troquel uno al lado del otro y permitir la integración de chiplets 2,5D en una plataforma interposer de bajo costo, la línea piloto NanoIC apunta a líneas de menos de 2 µm y ofrece tecnología de capa de redistribución de paso fino (FP RDL) basada en líneas y vías de cobre incrustadas en polímero.

Las tecnologías de interconexión, memoria y lógica de vanguardia antes mencionadas, definidas en dimensiones relevantes para la industria, están en el corazón de la línea piloto NanoIC. Lograrlos requiere la evaluación de nuevos procesos y materiales, requiere controles de proceso más estrictos y depende de un conjunto diverso de rutas de validación. La configuración de los módulos de proceso relevantes requiere una inversión en capacidades completamente nuevas en herramientas de procesamiento y medición. Estos módulos son los componentes básicos de un flujo de referencia y están sujetos a mejoras continuas para garantizar la maduración, aumentar la velocidad de aprendizaje e impulsar hacia TRL más altos. Un flujo de referencia constante representa una oportunidad de colaboración en I+D para ayudar a los proveedores de materiales y equipos a mantenerse a la vanguardia de la innovación.

Baje la barrera al diseño avanzado de chips con PDK avanzados

La línea piloto NanoIC proporciona acceso temprano a kits de diseño de procesos avanzados (PDK) para permitir a los diseñadores de la academia y la industria europeas explorar estos descubrimientos en lógica, memoria y tecnologías de interconexión.

Estos PDK son conjuntos de herramientas integrales que brindan a los diseñadores modelos predictivos, bibliotecas de celdas y recursos de integración a nivel de sistema para permitir una simulación y verificación precisas de circuitos integrados en nodos de tecnología avanzada. La disponibilidad de estos kits prácticos permite a los diseñadores de circuitos explorar las próximas arquitecturas de chips, abordar desafíos de diseño complejos y respaldar la innovación en el nodo de 2 nm y más allá.

Específicamente, la línea piloto NanoIC ofrece dos PDK complementarios. Uno es un PDK pionero para la exploración temprana del diseño de tecnologías IC de vanguardia, y el otro es un PDK de exploración de sistemas para allanar el camino para la creación de prototipos de hardware y la innovación a nivel de sistema.

Estos PDK se han lanzado a lo largo del proyecto e incluyen múltiples versiones del PDK de N2 Pathfinding, incluidas las versiones de los PDK lógicos A14 y A7. Si bien los PDK de memoria se basan en avances en eDRAM y SOT-MRAM, se pueden considerar soluciones de interconexión avanzadas a través de RDL, intercaladores de silicio y enlaces híbridos D2W.

Impulsando la innovación en Europa

La línea piloto NanoIC proporciona acceso flexible a tecnologías avanzadas de lógica, memoria y interconexión en todo el ecosistema de semiconductores. Empresas, institutos de investigación, startups y universidades pueden colaborar en función de sus necesidades de innovación.

Los fabricantes y fundiciones de dispositivos integrados pueden aprovechar la base para explorar nuevos módulos y opciones de mejora del rendimiento. Se invita a los proveedores europeos y mundiales de equipos y materiales a colaborar para que se puedan probar y perfeccionar nuevas herramientas y procesos utilizando la línea de base avanzada. Además, las empresas emergentes, las universidades y las empresas de diseño pueden acceder al PDK Pathfinding para la exploración temprana del diseño de futuros nodos y al PDK System Exploration para la creación de prototipos de hardware y la innovación a nivel de sistema. Además, la línea piloto NanoIC se dedica a capacitar a la próxima generación de profesionales de semiconductores. En asociación con los centros de competencia de la UE, ofrecemos cursos presenciales y virtuales sobre tecnologías más allá de 2 nm, desde materiales semiconductores hasta diseño de SoC. Nuestros programas prácticos de estudio y pasantías brindan a los estudiantes experiencia del mundo real, y la capacitación orientada a la industria prepara a nuestros estudiantes de licenciatura, maestría y doctorado para los desafíos del futuro. La Línea Piloto NanoIC está creando una fuerza laboral calificada para hacer avanzar la industria de semiconductores de Europa a través de cursos de expertos, capacitación técnica y campamentos de entrenamiento inmersivos.

En resumen, la línea piloto NanoIC está estratégicamente posicionada para cerrar la brecha entre la investigación de vanguardia y las aplicaciones comerciales en la industria de los semiconductores. El proyecto subraya el compromiso de Europa con la innovación, la competitividad y el crecimiento sostenible en un mundo cada vez más digital. El proyecto tiene como objetivo fortalecer el liderazgo de Europa en el mercado mundial de semiconductores mediante el avance de la tecnología y el fomento de la cooperación.

Descargo de responsabilidad

La adquisición y operación de la línea piloto NanoIC está financiada conjuntamente por Chips Joint Undertaining y los países participantes Bélgica (Flandes), Francia, Alemania, Finlandia, Irlanda y Rumanía a través de los programas Digital Europe (101183266) y Horizon Europe (101183277) de la Unión Europea. Para obtener más información, visite nanoic-project.eu.

Este artículo se basa en comentarios publicados en Nature Reviews Electrical Engineering (Volumen 1 | Diciembre de 2024 | 764–765 | 764).

Este artículo también se publicará en el número 24 de la revista trimestral.

Source link